Upcoming Workshops (Singapore)

Workshops for learning

For more details of the workshops, pls sent email to admin@launchxtec.com

Venue: Newcastle Australia Institute of Higher Education Singapore, 230 Victoria Street, #04-09/10, Bugis Junction Towers, S188024

Registration fee: SGD 800 per workshop (3 weeks before the workshop) and SGD 1,000 per workshop thereafter. We are pleased to offer the following discounts for block booking:

10% discount for registering for 3–5 workshops (any combination)

15% discount for registering for >5 workshops (any combination)

Please request a quotation by emailing admin@launchxtec.com or proceed with registration and payment via PayNow.

Breaking Down Fan-out Panel & Wafer-Level Packaging: Design, Assembly, and Competitive Technologies

(16-17 Apr 2026)

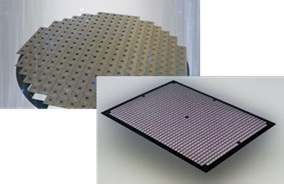

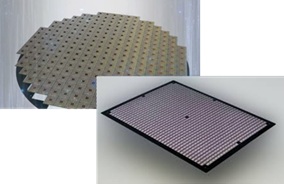

This workshop provides a comprehensive overview of chiplet-based and heterogeneous integration technologies, starting with IC packaging fundamentals, key market and technology drivers, and the industry shift from monolithic SoC toward modular SiP and chiplet architectures to enable scalability, performance, and design flexibility. It introduces Wafer Level Packaging with a focus on the limitations of Fan-In WLP and the advantages, evolution, and industry adoption of Fan-Out WLP as a critical enabler for high-density integration. Participants then explore wafer-level and panel-level FO-WLP through die-first and die-last architectures, real-world case studies from leading vendors, key assembly and reliability challenges, and future scaling toward PoP and panel-level manufacturing. The workshop concludes with an examination of emerging and competing technologies for advanced chiplet systems, including next-generation substrates, multi-dimensional packaging concepts, hybrid bonding, and glass core substrates, offering a forward-looking perspective on the future of advanced semiconductor packaging.

From PCB, Surface Mount Technology to joint reliability: PCB, SMT, soldering and its joint reliability

(25-26 May)

This comprehensive PCB & Assembly Excellence workshop offers an end-to-end technical deep dive designed to bridge the gap between initial design and high-reliability electronics manufacturing. Tailored for engineers and technicians, the program tracks the full lifecycle of a Printed Circuit Board, beginning with foundational material science (FR-4, polyimide, and CTE management) and progressing through precision fabrication flows like photolithography and advanced surface finishes. Participants will master high-density interconnect (HDI) strategies—including sequential build-up (SBU) and microvia stacking—while comparing the productivity of laser, plasma, and photo-via formation.

The curriculum further explores the critical physics of SMT assembly, from stencil aperture optimization to reflow profiling, before diving into the complex metallurgy of solder materials. By analyzing phase diagrams, IMC growth, and the performance of SnAgCu and Low-Temperature alloys, attendees will learn to predict and prevent failures. The workshop concludes with a rigorous focus on mechanical characterization and reliability, teaching you how to utilize ball shear testing and Weibull Distribution analysis to ensure your products withstand the thermal and mechanical stresses of real-world applications.

For workshop details, pls refer to the link

https://drive.google.com/file/d/13VQOFYusICXyIQXXopm8T7xwUIcTYdIB/view?pli=1

For workshop details, pls refer to the link

https://drive.google.com/file/d/1dUS8tQsCkJ5Gxew3I4eqrMUI67jjvzY7/view?pli=1

For workshop details, pls refer to the link

https://drive.google.com/open?id=173sFByNHJ8CcslxVryCZ6HQj2s8QPdJc&usp=drive_fs

For workshop details, pls refer to the link

https://drive.google.com/open?id=1N1oEjn0eCTBicOrui4uLkVglt4cGXf5o&usp=drive_fs

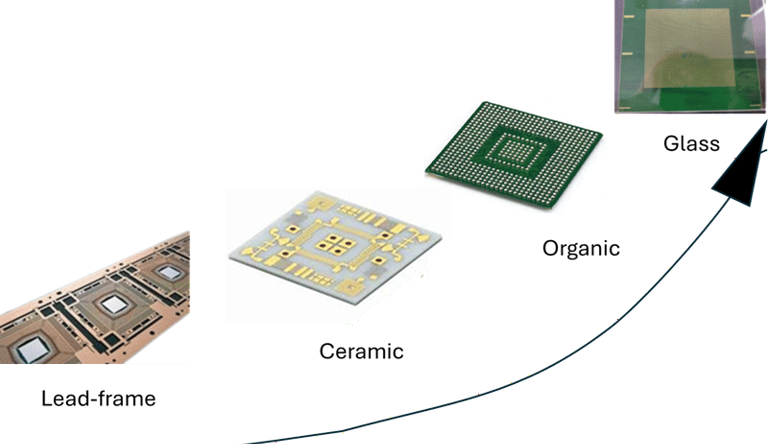

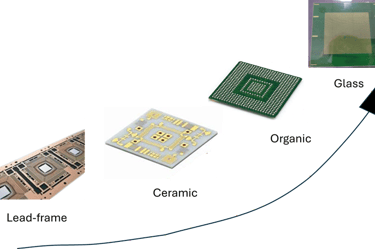

Semiconductor Packaging Substrate and Interposers: From Leadframe, Rigid to Glass Substrates

(25-26 Jun)

Elevate your technical edge in this comprehensive workshop exploring the full evolution of semiconductor packaging—from high-power leadframe and rigid substrate solutions to the glass-core innovations powering the AI and high-performance computing (HPC) revolution. Designed for packaging engineers and designers, this session provides a deep dive into the material science and fabrication flows of HTCC/LTCC ceramics and BT/ABF organic cores, contrasting their rugged performance against the high-bandwidth potential of Through-Glass Vias (TGV)

The curriculum tracks the shift from existing BT substrate from via fabrication, plating, and semi-additive patterning (SAP) to advanced glass core substrate like Laser Induced Deep Etching (LIDE) and precision metallisation. Beyond fabrication, you will tackle the critical assembly challenges that dictate yield—such as strip warpage, thermal stress, and adhesion management. By exploring the design constraints of CoWoS-S and SoIC architectures, you will gain the actionable expertise needed to successfully navigate the industry’s transition toward the next generation of high-density, thermally stable glass interposers.

Insight into Advanced Packaging and Trends for Business Executive

(23-24 Jul)

This Advanced Packaging Workshop is specifically designed for business executives to decode the strategic shift from traditional silicon design to the new frontier of Heterogeneous Integration. As Moore’s Law slows, the competitive edge has moved to the package, where Chiplets and 3D stacking now drive the performance gains once found only in the chip itself. This session strips away the technical jargon to focus on how architectures like CoWoS and Fan-Out are directly enabling the next generation of AI, 5G, and Automotive products while bypassing the soaring costs of monolithic chip manufacturing.

Through a commercial lens, the workshop provides critical supply chain intelligence and market-readiness insights. You will compare traditional assembly flows against modern System-in-Package (SiP) strategies to identify where value is captured and where risks reside in your roadmap. By understanding the transition to next-gen substrates and hybrid bonding, leaders will leave with the clarity needed to make high-stakes investment, sourcing, and partnership decisions in a landscape where packaging is now the primary driver of profitability and speed-to-market.